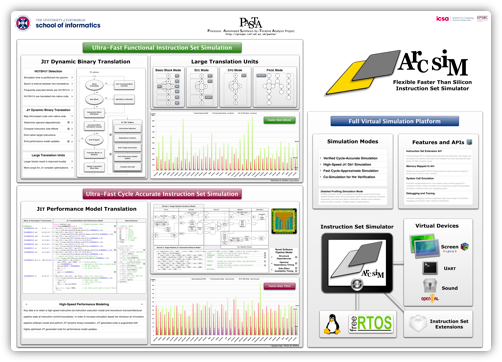

ArcSim is our 'Swiss army knife' for high-speed functional and cycle accurate instruction set simulation of the EnCore processor. It provides various simulation modes and yields a wealth of statistics and metrics about simulated programs.

Simulation Modes

- Cycle-Accurate Simulation mode allows for cycle-accurate simulation of our microarchitecture. This mode provides very detailed latency statistics for each instruction and has been calibrated using the EnCore processor.

- Fast Cycle-Approximate Simulation mode enables fast prediction of cycle counts based on information gathered during fast functional simulation and prior training.

- High-Speed Simulation mode uses Just-In-Time (JIT) Dynamic Binary Translation (DBT) techniques to create very high speed functional simulators capable of simulating an embedded system at speeds approaching (or even exceeding) real time. Recently we have extended our high-speed simulation mode with the capability of performing ultra-fast cycle accurate simulations by extending our JIT engine with the capability of augmenting JIT translated instructions with highly optimised cycle accurate code.

- Co-Simulation mode provides a Co-Simulation API used for hardware and performance verification.

- Register Tracking Simulation mode tracks read/write register access and the average distance (arithmetic mean, geometric mean) in instructions between a register access.

Other Features and APIs

- API for Instruction Set Extensions: simple plugin API for declaring PASTA instruction set extensions.

- API for Memory Mapped IO: simple and efficient API that allows one to hook custom code upon reads/writes to memory locations. We currently have the following implementation of memory mapped devices:

- Emulation of System Calls: There are emulation implementations for many system calls as well as support for redirection of standard streams such as stdin, stdout, and stderr.

- Debugging: Interactive debugging interface supporting single step tracing of instructions, debugging of processor state, setting of breakpoints, etc.

Publications

- I.Böhm, B.Franke and N.Topham

Cycle-Accurate Performance Modelling in an Ultra-Fast Just-In-Time Dynamic Binary Translation Instruction Set Simulator

Transactions on High-Performance Embedded Architectures and Compilers (HiPEAC'11), Volume 5, Issue 4, 2011. - O.Almer, I.Böhm, T.Edler von Koch, B.Franke, S.Kyle, V.Seeker, C.Thompson and N.Topham

Scalable Multi-Core Simulation Using Parallel Dynamic Binary Translation

To appear in Proceedings of the International Symposium on Systems, Architectures, Modeling, and Simulation (SAMOS'11), Samos, Greece, July 19-22, 2011. - I.Böhm, T.Edler von Koch, S.Kyle, B.Franke and N.Topham

Generalized Just-In-Time Trace Compilation using a Parallel Task Farm in a Dynamic Binary Translator

To Appear in ACM SIGPLAN 2011 Conference on Programming Language Design and Implementation (PLDI'11), San Jose, CA, June 2011. - I.Böhm, B.Franke and N.Topham

Cycle-Accurate Performance Modelling in an Ultra-Fast Just-In-Time Dynamic Binary Translation Instruction Set Simulator

Proceedings of the International Symposium on Systems, Architectures, Modeling, and Simulation (SAMOS'10), Samos, Greece, July 19-22, 2010. - D. Powell and B. Franke

Using Continuous Statistical Machine Learning to Enable High-Speed Performance Prediction in Hybrid Instruction-/Cycle-Accurate Instruction Set Simulators

Proceedings of the International Conference on Hardware/Software Codesign and System Synthesis (CODES-ISSS), October 2010, Grenoble, France. - D. Jones and N.P. Topham

High Speed CPU Simulation using LTU Dynamic Binary Translation

Proceedings of the 4th International HiPEAC Conference, Paphos, Cyprus, Jan. 25028, 2009. LNCS 5409, Springer 2009, ISBN 978-3-540-92989-5. - B. Franke

Fast Cycle-Approximate Instruction Set Simulation

Proceedings of the Workshop on Software & Compilers for Embedded Systems (SCOPES 2008), March 2008, Munich, Germany. - N.P. Topham and D. Jones

High Speed CPU Simulation using JIT Binary Translation

Proceedings of the 3rd Annual Workshop on Modeling, Benchmarking and Simulation, held in conjunction with ISCA-34, San Diego CA, June 2007.

ArcSim Poster