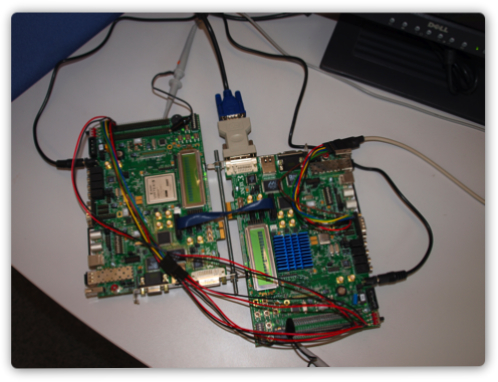

The EnCore processor and its SoC can be synthesized and run within an FPGA platform. This is currently based on the Xilinx Virtex-5 chip, and the ML507 board. This allows us to operate the EnCore processor at frequencies up to 75 MHz, and provides a range of I/O devices that are accessible to software.

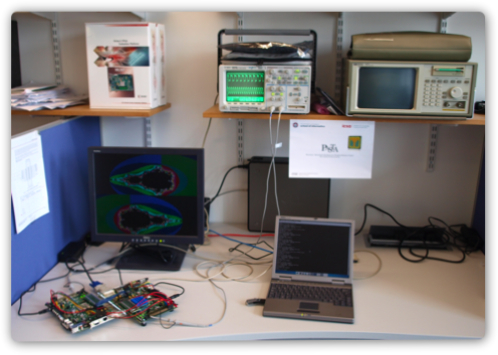

The above photograph shows the EnCore and its SoC executing a program that plots the Mandelbrot Set running on our FPGA platform. The Mandelbrot fractal program draws two fractals to the screen in 'parallel' using the Protothreads thread library. In order to calculate the colours and ASCII art characters for points in the Mandelbrot set we use fixed-point arithmetic, as the EnCore embedded processor does not have a floating point unit.

We use two FPGA boards: one runs the synthesized version of the EnCore processor [left board on picture], and the other runs synthesized RAMs [right board on picture].

Both compilation tool chains we developed and extended (i.e. our ECC and GCC compilers), are capable of emitting binaries that run on the FPGA platform. Loading of binaries as well as halting, starting, and debugging the processor is done via a JTAG interface.